Apollo Guidance Computer

Apollo Guidance Computer and DSKY | |

| Invented by | Charles Stark Draper Laboratory |

|---|---|

| Manufacturer | Raytheon |

| Introduced | August 1966 |

| Discontinued | July 1975 |

| Type |

|

| Processor | Discrete silicon integrated circuit (IC) chips (RTL based) |

| Frequency | 2.048 MHz |

| Memory |

|

| Ports | DSKY, IMU, Hand Controller, Rendezvous Radar (LM), Landing Radar (LM), Telemetry Receiver, Engine Command, Reaction Control System |

| Power consumption | 55 W[2]: 120 |

| Language | AGC Assembly Language |

| Weight | 70 lb (32 kg) |

| Dimensions | 24 in × 12.5 in × 6.5 in (61 cm × 32 cm × 17 cm) |

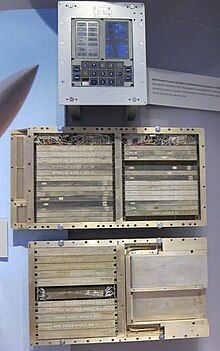

The Apollo Guidance Computer (AGC) was a digital computer produced for the Apollo program that was installed on board each Apollo command module (CM) and Apollo Lunar Module (LM). The AGC provided computation and electronic interfaces for guidance, navigation, and control of the spacecraft.[3] The AGC was the first computer based on silicon integrated circuits.[citation needed] The computer's performance was comparable to the first generation of home computers from the late 1970s, such as the Apple II, TRS-80, and Commodore PET.[4]

The AGC has a 16-bit word length, with 15 data bits and one parity bit. Most of the software on the AGC is stored in a special read-only memory known as core rope memory, fashioned by weaving wires through and around magnetic cores, though a small amount of read/write core memory is available.

Astronauts communicated with the AGC using a numeric display and keyboard called the DSKY (for "display and keyboard", pronounced "DIS-kee"). The AGC and its DSKY user interface were developed in the early 1960s for the Apollo program by the MIT Instrumentation Laboratory and first flew in 1966.[5]

Operation

[edit]Astronauts manually flew Project Gemini with control sticks, but computers flew most of Project Apollo except briefly during lunar landings.[6] Each Moon flight carried two AGCs, one each in the command module and the Apollo Lunar Module, with the exception of Apollo 7 which was an Earth orbit mission and Apollo 8 which did not need a lunar module for its lunar orbit mission. The AGC in the command module was the center of its guidance, navigation and control (GNC) system. The AGC in the lunar module ran its Apollo PGNCS (primary guidance, navigation and control system), with the acronym pronounced as pings.

Each lunar mission had two additional computers:

- The Launch Vehicle Digital Computer (LVDC) on the Saturn V booster instrumentation ring

- the Abort Guidance System (AGS, pronounced ags) of the lunar module, to be used in the event of failure of the LM PGNCS. The AGS could be used to take off from the Moon, and to rendezvous with the command module, but not to land.

Design

[edit]

The AGC was designed at the MIT Instrumentation Laboratory under Charles Stark Draper, with hardware design led by Eldon C. Hall.[2] Early architectural work came from J. H. Laning Jr., Albert Hopkins, Richard Battin, Ramon Alonso,[7] [8] and Hugh Blair-Smith.[9] The flight hardware was fabricated by Raytheon, whose Herb Thaler[10] was also on the architectural team.

According to Kurinec et al, the chips were welded onto the boards rather than soldered as might be expected.[11] Apollo Guidance Computer logic module drawings specify resistance-welding.[12][13]

Logic hardware

[edit]Following the use of integrated circuit (IC) chips in the Interplanetary Monitoring Platform (IMP) in 1963, IC technology was later adopted for the AGC.[14] The Apollo flight computer was the first computer to use silicon IC chips.[15]

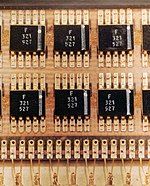

While the Block I version used 4,100 ICs, each containing a single three-input NOR gate, the later Block II version (used in the crewed flights) used about 2,800 ICs, mostly dual three-input NOR gates and smaller numbers of expanders and sense amplifiers.[16]: 27, 266 The ICs, from Fairchild Semiconductor, were implemented using resistor–transistor logic (RTL) in a flat-pack. They were connected via wire wrap, and the wiring was then embedded in cast epoxy plastic.[16]: 129

The use of a single type of IC (the dual NOR3) throughout the AGC avoided problems that plagued another early IC computer design, the Minuteman II guidance computer, which used a mix of diode–transistor logic and diode logic gates.[citation needed] NOR gates are universal logic gates from which any other gate can be made, though at the cost of using more gates.[17]

Memory

[edit]The computer had 2,048 words of erasable magnetic-core memory and 36,864 words of read-only core rope memory.[16]: 27, 90–93 Both had cycle times of 11.72 microseconds.[16]: 27 The memory word length was 16 bits: 15 bits of data and one odd-parity bit. The CPU-internal 16-bit word format was 14 bits of data, one overflow bit, and one sign bit (ones' complement representation).[16]: 35–37

DSKY interface

[edit]

The user interface to the AGC was the DSKY, standing for display and keyboard and usually pronounced "DIS-kee". It has an array of indicator lights, numeric displays, and a calculator-style keyboard. Commands were entered numerically, as two-digit numbers: Verb and Noun. Verb described the type of action to be performed and Noun specified which data were affected by the action specified by the Verb command.

Each digit was displayed via a green (specified as 530 nm[18]) high-voltage electroluminescent seven-segment display; these were driven by electromechanical relays, limiting the update rate. Three five-digit signed numbers could also be displayed in octal or decimal, and were typically used to display vectors such as space craft attitude or a required velocity change (delta-V). Although data was stored internally in metric units, they were displayed as United States customary units. This calculator-style interface was the first of its kind.

The command module has two DSKYs connected to its AGC: one located on the main instrument panel and a second located in the lower equipment bay near a sextant used for aligning the inertial guidance platform. The lunar module had a single DSKY for its AGC. A flight director attitude indicator (FDAI), controlled by the AGC, was located above the DSKY on the commander's console and on the LM.

Timing

[edit]The AGC timing reference came from a 2.048 MHz crystal clock. The clock was divided by two to produce a four-phase 1.024 MHz clock which the AGC used to perform internal operations. The 1.024 MHz clock was also divided by two to produce a 512 kHz signal called the master frequency; this signal was used to synchronize external Apollo spacecraft systems.

The master frequency was further divided through a scaler, first by five using a ring counter to produce a 102.4 kHz signal. This was then divided by two through 17 successive stages called F1 (51.2 kHz) through F17 (0.78125 Hz). The F10 stage (100 Hz) was fed back into the AGC to increment the real-time clock and other involuntary counters using Pinc (discussed below). The F17 stage was used to intermittently run the AGC when it was operating in the standby mode.

Central registers

[edit]The AGC had four 16-bit registers for general computational use, called the central registers:

- A: The accumulator, for general computation

- Z: The program counter – the address of the next instruction to be executed

- Q: The remainder from the

DVinstruction, and the return address afterTCinstructions - LP: The lower product after

MPinstructions

There were also four locations in core memory, at addresses 20–23, dubbed editing locations because whatever was stored there would emerge shifted or rotated by one bit position, except for one that shifted right seven bit positions, to extract one of the seven-bit interpretive op. codes that were packed two to a word. This was common to Block I and Block II AGCs.

Other registers

[edit]

The AGC had additional registers that were used internally in the course of operation:

- S: 12-bit memory address register, the lower portion of the memory address

- Bank/Fbank: 4-bit ROM bank register, to select the 1 kiloword ROM bank when addressing in the fixed-switchable mode

- Ebank: 3-bit RAM bank register, to select the 256-word RAM bank when addressing in the erasable-switchable mode

- Sbank (super-bank): 1-bit extension to Fbank, required because the last 4 kilowords of the 36-kiloword ROM was not reachable using Fbank alone

- SQ: 4-bit sequence register; the current instruction

- G: 16-bit memory buffer register, to hold data words moving to and from memory

- X: The 'x' input to the adder (the adder was used to perform all 1's complement arithmetic) or the increment to the program counter (Z register)

- Y: The other ('y') input to the adder

- U: Not really a register, but the output of the adder (the ones' complement sum of the contents of registers X and Y)

- B: General-purpose buffer register, also used to pre-fetch the next instruction. At the start of the next instruction, the upper bits of B (containing the next op. code) were copied to SQ, and the lower bits (the address) were copied to S.

- C: Not a separate register, but the ones' complement of the B register

- IN: Four 16-bit input registers

- OUT: Five 16-bit output registers

Instruction set

[edit]The instruction format used 3 bits for opcode, and 12 bits for address. Block I had 11 instructions: TC, CCS, INDEX, XCH, CS, TS, AD, and MASK (basic), and SU, MP, and DV (extra). The first eight, called basic instructions, were directly accessed by the 3-bit op. code. The final three were denoted as extracode instructions because they were accessed by performing a special type of TC instruction (called EXTEND) immediately before the instruction.

The Block I AGC instructions consisted of the following:

TC(transfer control)- An unconditional branch to the address specified by the instruction. The return address was automatically stored in the Q register, so the

TCinstruction could be used for subroutine calls. CCS(count, compare, and skip)- A complex conditional branch instruction. The A register was loaded with data retrieved from the address specified by the instruction. (Because the AGC uses ones' complement notation, there are two representations of zero. When all bits are set to zero, this is called plus zero. If all bits are set to one, this is called minus zero.) The diminished absolute value (DABS) of the data was then computed and stored in the A register. If the number was greater than zero, the DABS decrements the value by 1; if the number was negative, it is complemented before the decrement is applied—this is the absolute value. Diminished means "decremented but not below zero". Therefore, when the AGC performs the DABS function, positive numbers will head toward plus zero, and so will negative numbers but first revealing their negativity via the four-way skip below. The final step in

CCSis a four-way skip, depending upon the data in register A before the DABS. If register A was greater than 0,CCSskips to the first instruction immediately afterCCS. If register A contained plus zero,CCSskips to the second instruction afterCCS. Less than zero causes a skip to the third instruction afterCCS, and minus zero skips to the fourth instruction afterCCS. The primary purpose of the count was to allow an ordinary loop, controlled by a positive counter, to end in aCCSand aTCto the beginning of the loop, equivalent to an IBM 360'sBCT. The absolute value function was deemed important enough to be built into this instruction; when used for only this purpose, the sequence after theCCSwasTC*+2,TC*+2,ADONE. A curious side effect was the creation and use ofCCS-holes when the value being tested was known to be never positive, which occurred more often than one might suppose. That left two whole words unoccupied, and a special committee was responsible for assigning data constants to these holes. INDEX- Add the data retrieved at the address specified by the instruction to the next instruction.

INDEXcan be used to add or subtract an index value to the base address specified by the operand of the instruction that followsINDEX. This method is used to implement arrays and table look-ups; since the addition was done on both whole words, it was also used to modify the op. code in a following (extracode) instruction, and on rare occasions both functions at once. RESUME- A special instance of

INDEX(INDEX25). This is the instruction used to return from interrupts. It causes execution to resume at the interrupted location. XCH(exchange)- Exchange the contents of memory with the contents of the A register. If the specified memory address is in fixed (read-only) memory, the memory contents are not affected, and this instruction simply loads register A. If it is in erasable memory, overflow "correction" is achieved by storing the leftmost of the 16 bits in A as the sign bit in memory, but there is no exceptional behavior like that of

TS. CS(clear and subtract)- Load register A with the ones' complement of the data referenced by the specified memory address.

TS(transfer to storage)- Store register A at the specified memory address.

TSalso detects, and corrects for, overflows in such a way as to propagate a carry for multi-precision add/subtract. If the result has no overflow (leftmost 2 bits of A the same), nothing special happens; if there is overflow (those 2 bits differ), the leftmost one goes the memory as the sign bit, register A is changed to +1 or −1 accordingly, and control skips to the second instruction following theTS. Whenever overflow is a possible but abnormal event, theTSwas followed by aTCto the no-overflow logic; when it is a normal possibility (as in multi-precision add/subtract), theTSis followed byCAFZERO (CAF=XCHto fixed memory) to complete the formation of the carry (+1, 0, or −1) into the next higher-precision word. Angles were kept in single precision, distances and velocities in double precision, and elapsed time in triple precision. AD(add)- Add the contents of memory to register A and store the result in A. The 2 leftmost bits of A may be different (overflow state) before and/or after the

AD. The fact that overflow is a state rather than an event forgives limited extents of overflow when adding more than two numbers, as long as none of the intermediate totals exceed twice the capacity of a word. MASK- Perform a bit-wise (boolean) and of memory with register A and store the result in register A.

MP(multiply)- Multiply the contents of register A by the data at the referenced memory address and store the high-order product in register A and the low-order product in register LP. The parts of the product agree in sign.

DV(divide)- Divide the contents of register A by the data at the referenced memory address. Store the quotient in register A and the absolute value of the remainder in register Q. Unlike modern machines, fixed-point numbers were treated as fractions (notional decimal point just to right of the sign bit), so you could produce garbage if the divisor was not larger than the dividend; there was no protection against that situation. In the Block II AGC, a double-precision dividend started in A and L (the Block II LP), and the correctly signed remainder was delivered in L. That considerably simplified the subroutine for double precision division.

SU(subtract)- Subtract (ones' complement) the data at the referenced memory address from the contents of register A and store the result in A.

Instructions were implemented in groups of 12 steps, called timing pulses. The timing pulses were named TP1 through TP12. Each set of 12 timing pulses was called an instruction subsequence. Simple instructions, such as TC, executed in a single subsequence of 12 pulses. More complex instructions required several subsequences. The multiply instruction (MP) used 8 subsequences: an initial one called MP0, followed by an MP1 subsequence which was repeated 6 times, and then terminated by an MP3 subsequence. This was reduced to 3 subsequences in Block II.

Each timing pulse in a subsequence could trigger up to 5 control pulses. The control pulses were the signals which did the actual work of the instruction, such as reading the contents of a register onto the bus, or writing data from the bus into a register.

Memory

[edit]

Block I AGC memory was organized into 1 kiloword banks. The lowest bank (bank 0) was erasable memory (RAM). All banks above bank 0 were fixed memory (ROM). Each AGC instruction had a 12-bit address field. The lower bits (1-10) addressed the memory inside each bank. Bits 11 and 12 selected the bank: 00 selected the erasable memory bank; 01 selected the lowest bank (bank 1) of fixed memory; 10 selected the next one (bank 2); and 11 selected the Bank register that could be used to select any bank above 2. Banks 1 and 2 were called fixed-fixed memory, because they were always available, regardless of the contents of the Bank register. Banks 3 and above were called fixed-switchable because the selected bank was determined by the bank register.

The Block I AGC initially had 12 kilowords of fixed memory, but this was later increased to 24 kilowords. Block II had 36 kilowords of fixed memory and 2 kilowords of erasable memory.

The AGC transferred data to and from memory through the G register in a process called the memory cycle. The memory cycle took 12 timing pulses (11.72 μs). The cycle began at timing pulse 1 (TP1) when the AGC loaded the memory address to be fetched into the S register. The memory hardware retrieved the data word from memory at the address specified by the S register. Words from erasable memory were deposited into the G register by timing pulse 6 (TP6); words from fixed memory were available by timing pulse 7. The retrieved memory word was then available in the G register for AGC access during timing pulses 7 through 10. After timing pulse 10, the data in the G register was written back to memory.

The AGC memory cycle occurred continuously during AGC operation. Instructions needing memory data had to access it during timing pulses 7–10. If the AGC changed the memory word in the G register, the changed word was written back to memory after timing pulse 10. In this way, data words cycled continuously from memory to the G register and then back again to memory.

The lower 15 bits of each memory word held AGC instructions or data, with each word being protected by a 16th odd parity bit. This bit was set to 1 or 0 by a parity generator circuit so a count of the 1s in each memory word would always produce an odd number. A parity checking circuit tested the parity bit during each memory cycle; if the bit didn't match the expected value, the memory word was assumed to be corrupted and a parity alarm panel light was illuminated.

Interrupts and involuntary counters

[edit]The AGC had five vectored interrupts:

- Dsrupt was triggered at regular intervals to update the user display (DSKY).

- Erupt was generated by various hardware failures or alarms.

- Keyrupt signaled a key press from the user's keyboard.

- T3Rrupt was generated at regular intervals from a hardware timer to update the AGC's real-time clock.

- Uprupt was generated each time a 16-bit word of uplink data was loaded into the AGC.

The AGC responded to each interrupt by temporarily suspending the current program, executing a short interrupt service routine, and then resuming the interrupted program.

The AGC also had 20 involuntary counters. These were memory locations which functioned as up/down counters, or shift registers. The counters would increment, decrement, or shift in response to internal inputs. The increment (Pinc), decrement (Minc), or shift (Shinc) was handled by one subsequence of microinstructions inserted between any two regular instructions.

Interrupts could be triggered when the counters overflowed. The T3rupt and Dsrupt interrupts were produced when their counters, driven by a 100 Hz hardware clock, overflowed after executing many Pinc subsequences. The Uprupt interrupt was triggered after its counter, executing the Shinc subsequence, had shifted 16 bits of uplink data into the AGC.

Standby mode

[edit]The AGC had a power-saving mode controlled by a standby allowed switch. This mode turned off the AGC power, except for the 2.048 MHz clock and the scaler. The F17 signal from the scaler turned the AGC power and the AGC back on at 1.28 second intervals. In this mode, the AGC performed essential functions, checked the standby allowed switch, and, if still enabled, turned off the power and went back to sleep until the next F17 signal.

In the standby mode, the AGC slept most of the time; therefore it was not awake to perform the Pinc instruction needed to update the AGC's real time clock at 10 ms intervals. To compensate, one of the functions performed by the AGC each time it awoke in the standby mode was to update the real time clock by 1.28 seconds.

The standby mode was designed to reduce power by 5 to 10 W (from 70 W) during midcourse flight when the AGC was not needed. However, in practice, the AGC was left on during all phases of the mission and this feature was never used.

Data buses

[edit]The AGC had a 16-bit read bus and a 16-bit write bus. Data from central registers (A, Q, Z, or LP), or other internal registers could be gated onto the read bus with a control signal. The read bus connected to the write bus through a non-inverting buffer, so any data appearing on the read bus also appeared on the write bus. Other control signals could copy write bus data back into the registers.

Data transfers worked like this: To move the address of the next instruction from the B register to the S register, an RB (read B) control signal was issued; this caused the address to move from register B to the read bus, and then to the write bus. A WS (write S) control signal moved the address from the write bus into the S register.

Several registers could be read onto the read bus simultaneously. When this occurred, data from each register was inclusive-ORed onto the bus. This inclusive-OR feature was used to implement the Mask instruction, which was a logical AND operation. Because the AGC had no native ability to do a logical AND, but could do a logical OR through the bus and could complement (invert) data through the C register, De Morgan's theorem was used to implement the equivalent of a logical AND. This was accomplished by inverting both operands, performing a logical OR through the bus, and then inverting the result.

Software

[edit]

AGC software was written in AGC assembly language and stored on rope memory. The bulk of the software was on read-only rope memory and thus could not be changed in operation,[20] but some key parts of the software were stored in standard read-write magnetic-core memory and could be overwritten by the astronauts using the DSKY interface, as was done on Apollo 14.

A simple real-time operating system designed by J. Halcombe Laning[21] consisting of the 'Exec', a batch job-scheduling using cooperative multi-tasking,[22] and an interrupt-driven pre-emptive scheduler called the 'Waitlist' which scheduled timer-driven 'tasks', controlled the computer. Tasks were short threads of execution which could reschedule themselves for re-execution on the Waitlist, or could kick off a longer operation by starting a 'job' with the Exec. Calculations were carried out using the metric system, but display readouts were in units of feet, feet per second, and nautical miles – units that the Apollo astronauts were accustomed to.[23]

The AGC had a sophisticated software interpreter, developed by the MIT Instrumentation Laboratory, that implemented a virtual machine with more complex and capable pseudo-instructions than the native AGC. These instructions simplified the navigational programs. Interpreted code, which featured double precision trigonometric, scalar and vector arithmetic (16 and 24-bit), even an MXV (matrix × vector) instruction, could be mixed with native AGC code. While the execution time of the pseudo-instructions was increased (due to the need to interpret these instructions at runtime) the interpreter provided many more instructions than AGC natively supported and the memory requirements were much lower than in the case of adding these instructions to the AGC native language which would require additional memory built into the computer (in the 1960s memory was very expensive). The average pseudo-instruction required about 24 ms to execute. The assembler, named YUL for an early prototype Christmas Computer,[24] enforced proper transitions between native and interpreted code.

A set of interrupt-driven user interface routines called 'Pinball' provided keyboard and display services for the jobs and tasks running on the AGC. A set of user-accessible routines were provided to let the astronauts display the contents of various memory locations in octal or decimal in groups of 1, 2, or 3 registers at a time. 'Monitor' routines were provided so the operator could initiate a task to periodically redisplay the contents of certain memory locations. Jobs could be initiated.

The design principles developed for the AGC by MIT Instrumentation Laboratory, directed in late 1960s by Charles Draper, became foundational to software engineering—particularly for the design of more reliable systems that relied on asynchronous software, priority scheduling, testing, and human-in-the-loop decision capability.[25] When the design requirements for the AGC were defined, necessary software and programming techniques did not exist so they had to be designed from scratch. Many of the trajectory and guidance algorithms used were based on earlier work by Richard Battin.[21] The first command module flight was controlled by a software package called CORONA whose development was led by Alex Kosmala. Software for lunar missions consisted of COLOSSUS for the command module, whose development was led by Frederic Martin, and LUMINARY[26] on the lunar module led by George Cherry. Details of these programs were implemented by a team under the direction of Margaret Hamilton.[27] Hamilton was very interested in how the astronauts would interact with the software and predicted the types of errors that could occur due to human error.[22][27] In total, software development on the project comprised 1400 person-years of effort, with a peak workforce of 350 people.[21] In 2016, Hamilton received the Presidential Medal of Freedom for her role in creating the flight software.

The Apollo Guidance Computer software influenced the design of Skylab, Space Shuttle and early fly-by-wire fighter aircraft systems.[28][29]

The Apollo Guidance computer has been called "The fourth astronaut" for its role in helping the three astronauts who relied on it: Neil Armstrong, Buzz Aldrin and Michael Collins.[30]

Block II

[edit]A Block II version of the AGC was designed in 1966. It retained the basic Block I architecture, but increased erasable memory from 1 to 2 kilowords. Fixed memory was expanded from 24 to 36 kilowords. Instructions were expanded from 11 to 34 and I/O channels were implemented to replace the I/O registers on Block I. The Block II version is the one that actually flew to the moon. Block I was used during the uncrewed Apollo 4 and 6 flights, and was on board the ill-fated Apollo 1.

The decision to expand the memory and instruction set for Block II, but to retain the Block I's restrictive three-bit op. code and 12-bit address had interesting design consequences. Various tricks were employed to squeeze in additional instructions, such as having special memory addresses which, when referenced, would implement a certain function. For instance, an INDEX to address 25 triggered the RESUME instruction to return from an interrupt. Likewise, INDEX 17 performed an INHINT instruction (inhibit interrupts), while INDEX 16 reenabled them (RELINT). Other instructions were implemented by preceding them with a special version of TC called EXTEND. The address spaces were extended by employing the Bank (fixed) and Ebank (erasable) registers, so the only memory of either type that could be addressed at any given time was the current bank, plus the small amount of fixed-fixed memory and the erasable memory. In addition, the bank register could address a maximum of 32 kilowords, so an Sbank (super-bank) register was required to access the last 4 kilowords. All across-bank subroutine calls had to be initiated from fixed-fixed memory through special functions to restore the original bank during the return: essentially a system of far pointers.

The Block II AGC also has the EDRUPT instruction (the name is a contraction of Ed's Interrupt, after Ed Smally, the programmer who requested it). This instruction does not generate an interrupt, rather it performs two actions that are common to interrupt processing. The first action, inhibits further interrupts (and requires a RESUME instruction to enable them again). In the second action, the ZRUPT register is loaded with the current value of the program counter (Z). It was only used once in the Apollo software, for setting up the DAP cycle termination sequence in the Digital Autopilot of the lunar module.[31] It is believed to be responsible for problems emulating the LEM AGC Luminary software.

1201 and 1202 program alarms

[edit]

PGNCS generated unanticipated warnings during Apollo 11's lunar descent, with the AGC showing a 1202 alarm ("Executive overflow - NO CORE SETS"),[32] and then a 1201 alarm ("Executive overflow - NO VAC AREAS").[33] The response of the AGC to either alarm was a soft restart. The cause was a rapid, steady stream of spurious cycle steals from the rendezvous radar (tracking the orbiting command module), intentionally left on standby during the descent in case it was needed for an abort.[34][35]

During this part of the approach, the processor would normally be almost 85% loaded. The extra 6,400 cycle steals per second added the equivalent of 13% load, leaving just enough time for all scheduled tasks to run to completion. Five minutes into the descent, Buzz Aldrin gave the computer the command 1668, which instructed it to periodically calculate and display DELTAH (the difference between altitude sensed by the radar and the computed altitude).[nb 1] The 1668 added another 10% to the processor workload, causing executive overflow and a 1202 alarm. After being given the "GO" from Houston, Aldrin entered 1668 again and another 1202 alarm occurred. When reporting the second alarm, Aldrin added the comment "It appears to come up when we have a 1668 up". The AGC software had been designed with priority scheduling, and automatically recovered, deleting lower priority tasks including the 1668 display task, to complete its critical guidance and control tasks. Guidance controller Steve Bales and his support team that included Jack Garman issued several "GO" calls and the landing was successful.[36]

The problem was not a programming error in the AGC, nor was it pilot error. It was a peripheral hardware design bug that had already been known and documented by Apollo 5 engineers.[37] However, because the problem had only occurred once during testing, they concluded that it was safer to fly with the existing hardware that they had already tested, than to fly with a newer but largely untested radar system. In the actual hardware, the position of the rendezvous radar was encoded with synchros excited by a different source of 800 Hz AC than the one used by the computer as a timing reference. The two 800 Hz sources were frequency locked but not phase locked, and the small random phase variations made it appear as though the antenna was rapidly "dithering" in position, even though it was completely stationary. These phantom movements generated the rapid series of cycle steals.

J. Halcombe Laning's software and computer design saved the Apollo 11 landing mission. Had it not been for Laning's design, the landing would have been aborted for lack of a stable guidance computer.[37][38]

Applications outside Apollo

[edit]

The AGC formed the basis of an experimental fly-by-wire (FBW) system installed into an F-8 Crusader to demonstrate the practicality of computer driven FBW. The AGC used in the first phase of the program was replaced with another machine in the second phase, and research done on the program led to the development of fly-by-wire systems for the Space Shuttle. The AGC also led, albeit indirectly, to the development of fly-by-wire systems for the generation of fighters that were being developed at the time.[39]

Source code release

[edit]In 2003, Ron Burkey initiated the Virtual AGC Project, aiming to recover the Apollo Guidance Computer (AGC) source code and build a functional emulator.[40][41] As part of this project, the original code, transcribed and digitized from 1960s hard copies,[42] was made available through the Virtual AGC Project and MIT Museum.[43] This effort gained renewed attention in mid-2016 when former NASA intern Chris Garry uploaded the code to GitHub, generating significant media attention.[44][45][46]

See also

[edit]- Apollo PGNCS - the Apollo Primary Guidance and Navigation System

- AP-101 (IBM S/360-derived) computers used in the Space Shuttle

- Gemini Guidance Computer

- History of computer hardware

Notes

[edit]- ^ More specifically, verb 16 instructs the AGC to print the noun (in this case, 68, DELTAH) approximately twice per second. Had Aldrin known this, a simple 0668 (calculate and display DELTAH, once) would have only added approximately 5% load to the system, and would have only done so once, when ENTER was pressed.

References

[edit]- ^ Programmer's Manual, Block 2 AGC Assembly Language, retrieved 2018-08-27

- ^ a b Hall, Eldon C. (1996), Journey to the Moon: The History of the Apollo Guidance Computer, Reston, Virginia, USA: AIAA, p. 196, ISBN 1-56347-185-X

- ^ Interbartolo, Michael (January 2009). "Apollo Guidance, Navigation and Control Hardware Overview" (PDF).

- ^ "How did the Apollo flight computers get men to the moon and back ?". 11 March 2017.

- ^ James E. Tomayko (1988). "The Apollo guidance computer: Hardware". Computers in Spaceflight: The NASA Experience. NASA. Archived from the original on December 29, 2023.

- ^ Agle, D.C. (September 1998). "Flying the Gusmobile". Air & Space. Retrieved 2018-12-15.

- ^ "Ramon Alonso's introduction", AGC History Project (Caltech archive, original site closed), MIT, July 27, 2001, retrieved 2009-08-30

- ^ "Ramon Alonso's interview (Spanish)", Ramón Alonso, el argentino que llevó a la Apollo 11 a la Luna, Diario La Nacion, March 7, 2010

- ^ "Hugh Blair-Smith biography", AGC History Project (Caltech archive, original site closed), MIT, January 2002, retrieved 2009-08-30

- ^ "Herb Thaler introduction", AGC History Project (Caltech archive, original site closed), MIT, 14 September 2001, retrieved 2009-08-30

- ^ Kurinec, Santosh K; Indovina, Mark; McNulty, Karl; Seitz, Matthew (2021). "Recreating History: Making the Chip that went on the Moon in 1969 on Apollo 11" (PDF). Rochester Institute of Technology. p. 9. Retrieved 29 August 2023.

- ^ "LOGIC MODULE ASSEMBLY NO. A1-A16". MIT Instrumentation Lab. July 11, 1963. p. Sheet 1 of 2, Note 2.

- ^ "Apollo Requirements for Process Control and Fabrication of Resistance-Welded Electronic Circuit Modules and Assemblies". Archive.org. NASA. May 22, 1963. Retrieved 19 February 2024.

- ^ Butrica, Andrew J. (2015). "Chapter 3: NASA's Role in the Manufacture of Integrated Circuits". In Dick, Steven J. (ed.). Historical Studies in the Societal Impact of Spaceflight (PDF). NASA. pp. 149–250. ISBN 978-1-62683-027-1.

- ^ "Apollo Guidance Computer and the First Silicon Chips". National Air and Space Museum. Smithsonian Institution. 14 October 2015. Retrieved 1 September 2019.

- ^ a b c d e Hall, Eldon C. (1972). MIT's Role in Project Apollo: Final report on contracts NAS 9-163 and NAS 94065 (PDF). Cambridge, MA: MIT. Retrieved 15 June 2021.

- ^ Peirce, C. S. (manuscript winter of 1880–81), "A Boolian Algebra with One Constant", published 1933 in Collected Papers v. 4, paragraphs 12–20. Reprinted 1989 in Writings of Charles S. Peirce v. 4, pp. 218–21, Google [1]. See Roberts, Don D. (2009), The Existential Graphs of Charles S. Peirce, p. 131.

- ^ "Apollo DSKY panel relight: The full story". YouTube. 27 July 2021.

- ^ Weinstock, Maia (2016-08-17). "Scene at MIT: Margaret Hamilton's Apollo code". MIT News. Retrieved 2016-08-17.

- ^ Mindell 2008, pp. 154, 157.

- ^ a b c Hoag, David (September 1976). "The History of Apollo On-board Guidance, Navigation, and Control" (PDF). Charles Stark Draper Laboratory.

- ^ a b Mindell 2008, p. 149.

- ^ "The Moon landings". UK Metric Association. 18 October 2018.

- ^ "Hugh Blair-Smith's Introduction", AGC History Project (Caltech archive, original site closed), MIT, 30 November 2001, retrieved 2010-03-21

- ^ "NASA Honors Apollo Engineer" (Press release). September 3, 2003.

- ^ "Virtual AGC Luminary Page".

- ^ a b Harvey IV, Harry Gould (13 October 2015). "Her Code Got Humans on the Moon—And Invented Software Itself". WIRED. Retrieved 2018-11-25.

- ^ "About Margaret Hamilton". NASA Office of Logic Design. February 3, 2010.

- ^ A.J.S. Rayl. "NASA Engineers and Scientists-Transforming Dreams Into Reality". Archived from the original on May 16, 2016.

- ^ Fong, Kevin (2019). "13 minutes to the moon: Episode 5 The fourth astronaut". bbc.co.uk. BBC World Service.

- ^ O'Brien, Frank (2010-06-25). The Apollo Guidance Computer: Architecture and Operation. Springer Science & Business Media. ISBN 978-1-4419-0877-3.

- ^ Collins, Michael; Aldrin, Edwin (1975), Cortright, Edgar M. (ed.), "A Yellow Caution Light", NASA SP-350, Apollo Expeditions to the Moon, Washington, DC: NASA, pp. Chapter 11.4, ISBN 978-0486471754, retrieved 2009-08-30

- ^ "chrislgarry/Apollo-11". GitHub. Retrieved 2016-07-17.

- ^ Adler, Peter (1998), Jones, Eric M. (ed.), "Apollo 11 Program Alarms", Apollo 11 Lunar Surface Journal, NASA, retrieved 2009-09-01

- ^ Martin, Fred H. (July 1994), Jones, Eric M. (ed.), "Apollo 11 : 25 Years Later", Apollo 11 Lunar Surface Journal, NASA, retrieved 2009-09-01

- ^ Cortright, Edgar M., ed. (1975), "The Lunar Module Computer", Apollo 11 Lunar Surface Journal, NASA, retrieved 2010-02-04

- ^ a b Eyles, Don (February 6, 2004), "Tales From The Lunar Module Guidance Computer", 27th annual Guidance and Control Conference, Breckenridge, Colorado: American Astronautical Society

- ^ Witt, Stephen (June 24, 2019). "Apollo 11: Mission Out of Control". Wired. San Francisco: Condé Nast Publications. Retrieved September 18, 2019.

- ^ Tomayko, James E. (2000), "NASA SP-2000-4224 — Computers Take Flight: A History of NASA's Pioneering Digital Fly-By-Wire Project" (PDF), The NASA History Series, Washington, D.C.: NASA, retrieved 2009-09-01

- ^ Burkey, Ron. "VirtualAGC". iBiblio. Retrieved 10 April 2021.

- ^ "AGC source code collection on Github, maintained by iBiblio". GitHub. Archived from the original on 7 May 2021. Alt URL

- ^ "Archiving and referencing the Apollo source code". www.softwareheritage.org. Retrieved 2021-09-09.

- ^ "Virtual AGC Home Page". ibiblio.org. Retrieved 2021-09-09.

- ^ Collins, Keith (9 July 2016). "The code that took America to the moon was just published to GitHub, and it's like a 1960s time capsule". Quartz. Retrieved 19 August 2016.

- ^ Garry, Chris. "Original Apollo 11 Guidance Computer (AGC) source code for the command and lunar modules". GitHub. Archived from the original on 12 April 2021. Alt URL

- ^ "Apollo 11's source code is now on GitHub". Engadget. 10 July 2016. Retrieved 2021-09-09.

Sources

[edit]- Mindell, David A. (2008). Digital Apollo: Human and Machine in Spaceflight. Cambridge, Massachusetts: The MIT Press. ISBN 978-0-262-26668-0.

External links

[edit]- Documentation on the AGC and its development

- AGC4 Memo #9, Block II Instructions – The infamous memo that served as de facto official documentation of the instruction set

- Computers in Spaceflight: The NASA Experience – By James Tomayko (Chapter 2, Part 5, The Apollo guidance computer: Hardware)

- Computers Take Flight – By James Tomayko

- The Apollo Guidance Computer - A Users View (PDF) – By David Scott, Apollo mission astronaut

- Lunar Module Attitude Controller Assembly Input Processing (PDF) – By José Portillo Lugo, History of Technology

- The MIT AGC Project – With comprehensive document archive

- Luminary software source code listing, for Lunar Module guidance computer. (nb. 622 Mb)

- Colossus software source code listing, for Command Module guidance computer. (nb. 83 Mb)

- National Air and Space Museum's AGC Block I and Dsky

- Annotations to Eldon Hall's Journey to the Moon – An AGC system programmer discusses some obscure details of the development of AGC, including specifics of Ed's Interrupt

- Documentation of AGC hardware design, and particularly the use of the new integrated circuits in place of transistors

- Documentation of AGC software operation

- Delco Electronics, Apollo 15 - Manual for CSM and LEM AGC software used on the Apollo 15 mission, including detailed user interface procedures, explanation of many underlying algorithms and limited hardware information. Note that this document has over 500 pages and is over 150 megabytes in size.

- Source code for Command Module code (Comanche054) and Lunar Module code (Luminary099) as text.

- GitHub Complete Source Code Original Apollo 11 Guidance Computer (AGC) source code for the command and lunar modules.

- Some AGC-based projects and simulators

- AGC Replica – John Pultorak's successful project to build a hardware replica of the Block I AGC in his basement. Mirror site: AGC Replica.

- Virtual AGC Home Page – Ronald Burkey's AGC simulator, plus source and binary code recovery for the Colossus (CSM) and Luminary (LEM) SW.

- Moonjs – A web-based AGC simulator based on Virtual AGC.

- Eagle Lander 3D Shareware Lunar Lander Simulator with a working AGC and DSKY (Windows only).

- AGC restarted 45 years later – youtube

Feature Stories

- Computer for Apollo(1965) MIT Science Reporter – youtube

- Weaving the way to the Moon (BBC News)

- Restorers try to get lunar module guidance computer up and running (Wall Street Journal)

- Computer for Apollo video – youtube